FPGA設計

長年の自社製品開発により培った装置開発技術を基に、最適なソリューションをご提供いたします。

| デバイスベンダ | XILINX | ALTERA | Lattice |

|---|---|---|---|

| 開発ツール | ISE (XILINX) | Quartus II PRIME | ispLEVER |

| 設計言語 | VHDL、VerilogHDL | ||

| 論理シミュレータ | ModelSim PE | ||

| デバイスの使用実績 |

Virtex-4 Virtex-5 Virtex-6 Spartan3A |

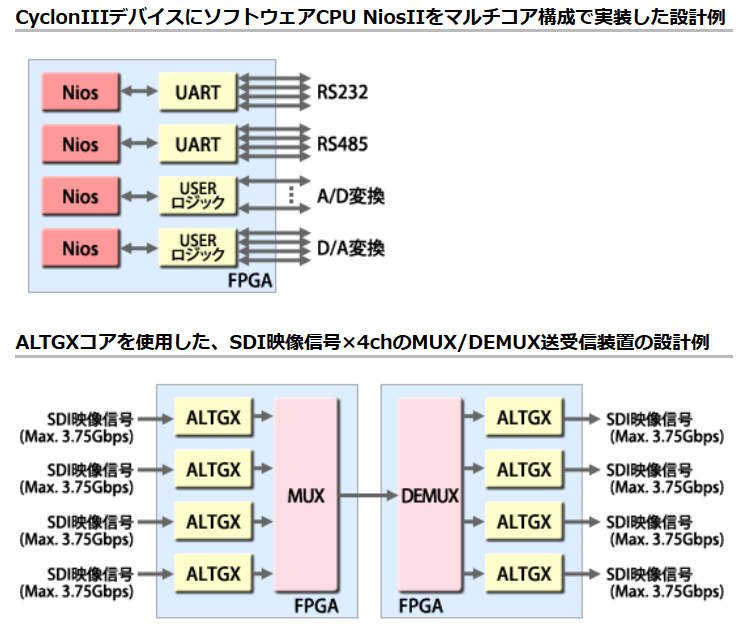

Stratix II ArriaII GX Cyclone III、IV MAX10 (CPLD) |

MACH系 (CPLD) XP2(CPLD) |

| ソフトコアCPU | - | Nios II | - |

FPGA設計例

| プリント基板外観検査機 | 輪郭追跡法画像処理エンジン、×字/+字側長 |

|---|---|

| CameraLink、DRAM、PCI I/F、NiosⅡ | |

| LCD検査機 | 隣接比較検査、DRC検査 |

| コントラスト強調/シェーディング補正/ノイズ除去/移動平均 | |

| メディアンフィルタ/エッジ強調/膨張/圧縮/平滑/細線化等 | |

| 通信関連 | HDLC通信 |

| ECC |

お問い合わせ

株式会社協栄システム

〒140-0002 東京都品川区東品川4-12-6

品川シーサイドキャナルタワー

品川シーサイドキャナルタワー

〈 本部 〉

03-4241-8856(代表)

(受付時間 : 平日 午前8時45分~午後5時30分)

03-5479-3566